# INTIBITATION OF THE PROPERTY O

John McHale Radar

Field Intelligence Radar's brave new world: OSA

Mil Tech Insider SiGe ADCs/DACs for EW

**Legacy Software Migration**Static analysis meets legacy S/W

Paul Anderson, GrammaTech

Jan/Feb 2013 Volume 9 | Number 1

processors drive radar signal processing

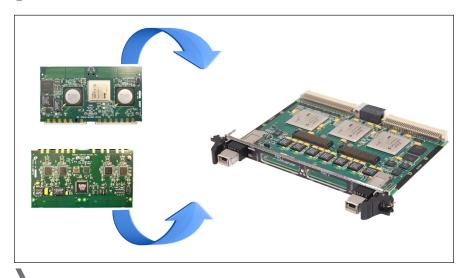

# Annapolis Micro Systems

The FPGA Systems Performance Leader

# High Performance Signal and Data Processing in Scalable FPGA Computing Fabric

GEOINT, Ground Stations, SDR, Radar, Sigint, COMINT, ELINT, DSP, Network Analysis, Encryption, Image Processing, Pattern Matching, Oil & Gas Exploration, Financial Algorithms, Genomic Algorithms

Direct Seamless Connections with no Data Reduction

Between External Sensors and FPGAs

Between FPGAs and Processors over IB or 10GE

Between FPGAs and Standard Output Modules

Between FPGAs and Storage Arrays

Ultimate Modularity

From 1 to 8 Virtex 4, 5 or 6 FPGA/Memory Modules

Input/Output Modules Include:

Quad 130 MSPS thru Quad 550 MSPS A/D

1.5 GSps thru 5.0 GSps A/D, Quad 600 MSps D/A,

Dual 1.5 GSps thru 4.0 GSps D/A

Infiniband, 10G, 40G or 100G Ethernet or SFPDP

VME/VXS/VPX, IBM Blade, PCI-X/PCI Express, PMC/XMC, MicroTCA

No Other FPGA Board Vendor Streams This Volume of Data Real Time Straight Into the Heart of the Processing Elements and Then Straight Back Out Again

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com USA (410) 841-2514 www.annapmicro.com

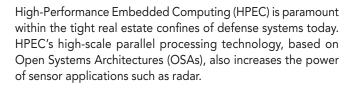

A 1.66GHz Intel®Atom™ Mil/COTS SBC of EPIC Proportions

The EPX-C380 is a rugged single board computer that provides an open powerful platform for harsh Mil/COTS applications. Powered with either a single or dual core processor, it has a wealth of onboard I/O plus expansion options. Also it supports Linux, Windows® XP embedded, and other x86 real-time operating systems.

1.66GHz Intel® Atom™ N450 single core or D510 dual core processor available

Embedded Gen 3.5+ GFX video core supports CRT and LVDS flat panels simultaneously

- Custom splash screen on start up

- · Optional 1MB of battery backed SRAM

- · Two Gigabit Ethernet ports

- Two SATA channels

- Eight USB 2.0 ports

- Four serial RS-232/422/485 channels

- 48 bi-directional digital I/O lines

- CompactFlash (CF) card supported

- MiniPCle and PC/104-Plus expansion connectors

- High Definition audio supported (7.1)

- WDT, RTC, LPT, status LEDs, and beeper

- +5 volt only operation

- EPIC sized: 4.5" x 6.5" and RoHS compliant

- EBX form factor SBC also available

- Extended temperature operation

- · Responsive and knowledgeable technical support

- Long-term product availability

- Quick Start Kits for software development

Contact us for additional information, pricing, and custom configurations. Our factory application engineers look forward to working with you.

Call 817-274-7553 or Visit www.winsystems.com/EPX-C380MR

Ask about our 30-day product evaluation

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

# www.mil-embedded.com Vilitary EMBEDDED SYSTEMS

### ON THE COVER:

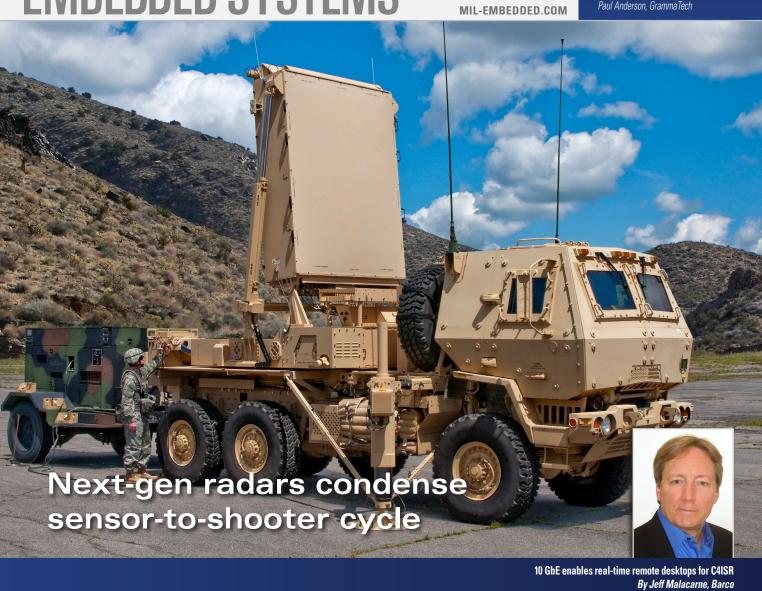

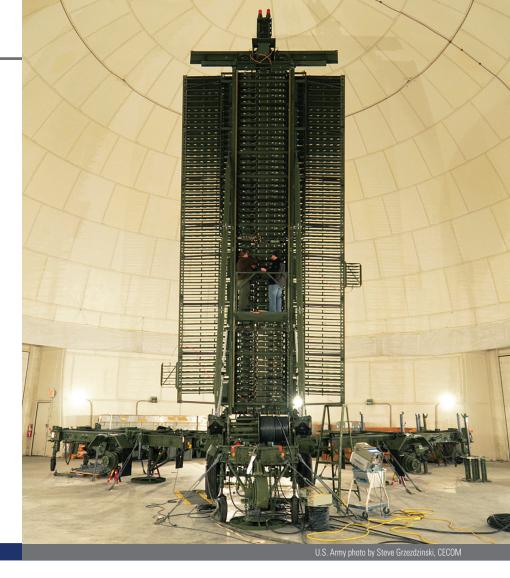

Top photo: The AN/TPQ-53 (Q-53) counterfire target acquisition radar from Lockheed Martin provides 360-degree protection from mortar, rocket, and artillery fire - tracking targets in their upward path and enabling a counterattack before the projectile makes impact. Photo courtesy of Lockheed Martin

Bottom photo: Radar onboard U.S. Navy Aegis-class ships uses PowerStream technology from Mercury Systems for radar signal processing. Photo courtesy of Lockheed Martin

January/February 2013

Volume 9

### **COLUMNS**

### **Editor's Perspective**

Radar, electronic warfare steadier parts of military market By John McHale

### Field Intelligence

Radar's brave new world: OSA By Charlotte Adams

### Mil Tech Insider

SiGe-based ADCs/DACs double COTS Electronic Warfare processing performance By David Jednyak

### **Legacy Software Migration**

Static analysis exposes latent defects 10 in legacy software By Paul Anderson, GrammaTech

45 Editor's Choice Products

### **E-CASTS**

http://ecast.opensystemsmedia.com

### Radar and electronic warfare drive signal processing innovation

Feb. 27, 12pm MST Presented by: Altera, Pentek, Inc., Mercury, Rohde & Schwarz

### Managing safety and security through open architectures

March 26, 11am MST Presented by: Esterel, GE Intelligent Platforms, RTI, Wind River

### **WEB RESOURCES**

Subscribe to the magazine or E-letter Live industry news | Submit new products http://submit.opensystemsmedia.com

White papers:

Read: http://whitepapers.opensystemsmedia.com Submit: http://submit.opensystemsmedia.com

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

© 2013 OpenSystems Media © 2013 Military Embedded Systems ISSN: Print 1557-3222

### **SPECIAL REPORT | Radar design trends**

- 12 Next-gen radars: Seeing through the clutter By John McHale

- 16 Two-phase cooling meets the challenges of modern radar applications By Dan Kinney and Andy Johnston, Parker Hannifin Corp.

### MIL TECH TRENDS | Signal processing trends in radar, sonar, and electronic warfare

- 20 Fast processors, FPGAs fuel radar/EW signal processing performance By John McHale

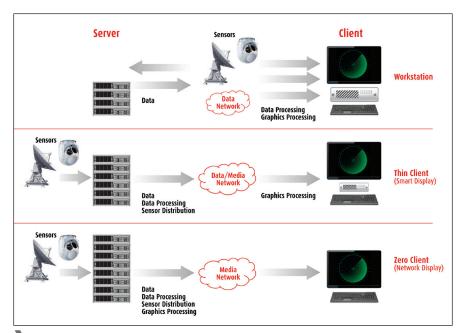

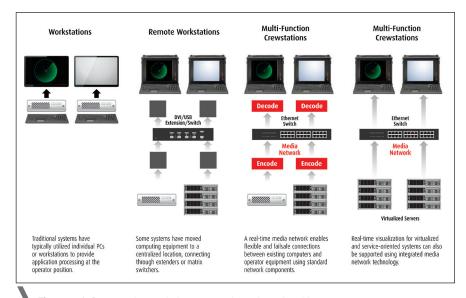

- 10 GbE enables real-time remote desktops for C4ISR 26 By Jeff Malacarne, Barco

- 30 Exploiting MOSA software for high-performance ISR and signal processing applications By Michael Stern, GE Intelligent Platforms

- 34 MOSA provides cost savings, performance, flexibility for EW digital receivers By Chris Lewis and Alton Graves, Mercury Defense Systems

### **INDUSTRY SPOTLIGHT |** Reconfigurable computing for

radar systems

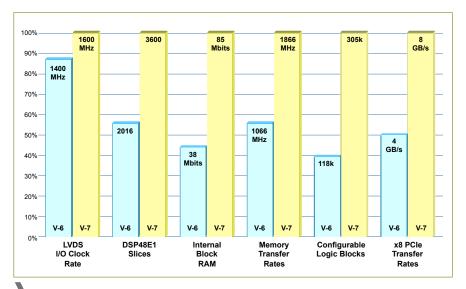

38 Virtex-7 FPGA technology boosts radar performance By Rodger Hosking, Pentek, Inc.

# **SEARCHING FOR Intel® Core™ i7 PROCESSOR SOLUTIONS?**

# Your search is over!

CompactPCI • COM Express • VME • PrPMC/XMC • VPX • Custom

X-ES delivers the latest 3rd generation Intel Core i7 processor solutions on the widest range of standard and custom form factors in the industry. With our proven record of meeting aggressive schedules, you can count on X-ES to deliver Intel Core i7 processor solutions on time, and with unparalleled customer support. Call us today to learn more.

| DVER  | TISER INFORMATION                                                                                                |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Page  | Advertiser/Ad Title                                                                                              |  |  |  |  |  |  |

| 29    | Aitech Defense Systems –<br>Our technology investments protect<br>yours                                          |  |  |  |  |  |  |

| 41    | Alphi Technology Corporation –<br>Looking for I/O for your mission<br>computer?                                  |  |  |  |  |  |  |

| 37    | <b>Altera Corporation</b> – Altera Stratix V GS FPGAs                                                            |  |  |  |  |  |  |

| 42    | Altera Corporation – Enabling<br>advanced designs for radar and<br>electronic warfare systems with<br>FPGAs      |  |  |  |  |  |  |

| 2     | Annapolis Micro Systems, Inc. –<br>High performance signal and data<br>processing                                |  |  |  |  |  |  |

| 37    | Annapolis Micro Systems, Inc. – WILD storage solution                                                            |  |  |  |  |  |  |

| 37    | Annapolis Micro Systems, Inc. – WILD OpenVPX switch                                                              |  |  |  |  |  |  |

| 13    | <b>Blue Pearl Software</b> – Is your FPGA design signoff quality?                                                |  |  |  |  |  |  |

| 43    | Creative Electronic Systems – Prospects of COTS products for future radar systems – challenges and opportunities |  |  |  |  |  |  |

| 40    | DiSTI – Interface with reality                                                                                   |  |  |  |  |  |  |

| 17    | Elma Electronic – Systems –<br>Small is the new big!                                                             |  |  |  |  |  |  |

| 46    | Embedded World – It's a smarter world                                                                            |  |  |  |  |  |  |

| 11    | Enginasion Inc. – Engineering imagination                                                                        |  |  |  |  |  |  |

| 15    | Excalibur Systems, Inc. –<br>MACCsimize your data conversion<br>ability                                          |  |  |  |  |  |  |

| 47    | GE Intelligent Platforms, Inc. –<br>High-performance radar with<br>out-of-box readiness                          |  |  |  |  |  |  |

| 37    | <b>GSI Technology</b> – Ultra-high<br>performance memories from<br>GSI Technology                                |  |  |  |  |  |  |

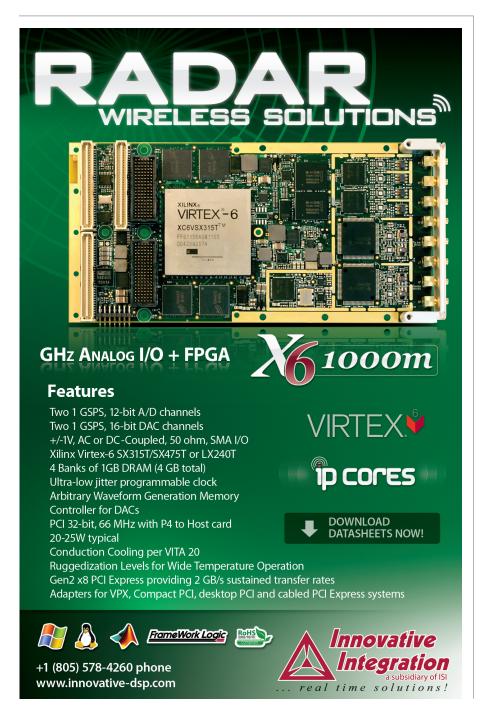

| 14    | Innovative Integration –<br>Radar wireless solutions                                                             |  |  |  |  |  |  |

| 19    | Interface Concept – Switches and IP routers                                                                      |  |  |  |  |  |  |

| 24-25 | Mercury Systems – Today we become<br>Mercury Systems                                                             |  |  |  |  |  |  |

| 48    | Pentek, Inc. – Critical recording in any arena                                                                   |  |  |  |  |  |  |

| 40    | Phoenix International –<br>Introducing RPC24                                                                     |  |  |  |  |  |  |

# Military embedded systems

### Military Embedded Systems Editorial/Production Staff

John McHale, Editorial Director imchale@opensystemsmedia.com

Sharon Hess, Managing Editor sharon\_hess@opensystemsmedia.com Steph Sweet, Creative Director ssweet@opensystemsmedia.com

### Sales Group

Tom Varcie

Senior Account Manager tvarcie@opensystemsmedia.com

Rebecca Barker

Strategic Account Manager rbarker@opensystemsmedia.com

Eric Henry

Strategic Account Manager ehenry@opensystemsmedia.com

Ann Jesse, Strategic Account Manager ajesse@opensystemsmedia.com

Christine Long

Vice President, Online Business clong@opensystemsmedia.com

### Reprints and PDFs

republish@opensystemsmedia.com

### International Sales

Elvi Lee, Account Manager - Asia elvi@aceforum.com.tw

Gerry Rhoades-Brown Account Manager - Europe gerry.rhoadesbrown@husonmedia.com

### **Regional Sales Managers**

Barbara Quinlan, Southwest bquinlan@opensystemsmedia.com

Denis Seger, Southern California dseger@opensystemsmedia.com

Sydele Starr Northern California sstarr@opensystemsmedia.com

Ron Taylor East Coast/Mid Atlantic

rtaylor@opensystemsmedia.com

### OpenSystems Media Editorial/Production Staff

DSP-FPGA.com Embedded Control Moustrial Military Small formfactors VITA-TECHNOLOGIES

John McHale, Editorial Director Military Embedded Systems jmchale@opensystemsmedia.com

Sharon Hess, Managing Editor Military Embedded Systems Embedded Computing Design Industrial Embedded Systems sharon\_hess@opensystemsmedia.com

Jim Turley, Embedded Moderator Embedded Computing Design iturley@opensystemsmedia.com

Mike Demler, Editorial Director EDA Digest, DSP-FPGA.com mdemler@opensystemsmedia.com

Joe Pavlat, Editorial Director xTCA and CompactPCI Systems jpavlat@opensystemsmedia.com

Jerry Gipper, Editorial Director VITA Technologies jgipper@opensystemsmedia.com Warren Webb, Editorial Director Embedded Computing Design Industrial Embedded Systems wwebb@opensystemsmedia.com

Monique DeVoe, Assistant Managing Editor VITA Technologies **EDA Digest**

DSP-FPGA.com

mdevoe@opensystemsmedia.com

Brandon Lewis, Associate Editor xTCA and CompactPCI Systems PC/104 and Small Form Factors blewis@opensystemsmedia.com

Curt Schwaderer, Technology Editor

Steph Sweet, Creative Director David Diomede, Art Director

Joann Toth, Senior Designer

Konrad Witte, Senior Web Developer

Matt Jones, Web Developer

### **Editorial/Business Office**

Patrick Hopper, Publisher Tel: 586-415-6500 phopper@opensystemsmedia.com

### **Subscriptions Updates**

Karen Layman, Business Manager www.opensystemsmedia.com/subscriptions Tel: 586-415-6500 ■ Fax: 586-415-4882 30233 Jefferson, St. Clair Shores, MI 48082 Rosemary Kristoff, President rkristoff@opensystemsmedia.com

Wayne Kristoff, CTO

16626 E. Avenue of the Fountains, Ste. 201 Fountain Hills, AZ 85268 Tel: 480-967-5581 Fax: 480-837-6466

37

44

37

3

5

processor solutions?

analysis

proportions

Rakon - Digital Pulse Compression

Rakon - Radar retrofits, subsystems

Spectracom Corporation - Fast and

affordable microwave frequency

WinSystems, Inc. - A 1.66 GHz

Intel Atom Mil/COTS SBC of EPIC

X-ES - Searching for Intel Core i7

Sub-Systems (DPCSS)

are key in today's market

# Radar, electronic warfare steadier parts of military market

By John McHale, Editorial Director

"Uncertain" was the keyword most of our readers and advertisers attached to the outlook for electronics funding and defense spending worldwide last year. Threats of sequestration and a stagnant global economy fueled the doubt, which unfortunately continues today. The sequestration threat was only postponed, not removed. However, if Department of Defense (DoD) spending were to be dramatically slashed in such a scenario, many feel sensor procurement and development - specifically radar and electronic warfare technology would remain strong.

As we reduce our military footprint worldwide, we will rely more than ever on sensor data from Intelligence, Surveillance, and Reconnaissance (ISR) systems onboard unmanned aircraft, in satellites, and on the ground. Accurate, real-time information from radar and other sensors is crucial to improving situational awareness. Improving bandwidth in military systems is of equal importance because it will help reduce the sensor to shooter cycle - the time it takes for sensor data to reach a shooter so it can eliminate a threat.

High-performance radar systems will need to provide much of the key intelligence to the warfighter. Radar requirements coming out of the DoD are calling for detection of small, slow-moving objects such as dismounted individuals on the ground and obscure targets in littoral waters. Market numbers show how much activity occurred in military radar contracts just in 2012 alone - indicating radar technology might be the best bet for military electronics investment over the next few years. According to Brad Curran, an analyst with Frost & Sullivan in San Antonio, TX, U.S. radar contracts for 2012 totaled \$4.26 billion, an increase of almost a \$1 billion over 2011 and about \$1.5 billion over 2010 numbers. The U.S. radar market has shown significant increases the past

three years, driven mostly by missile defense and the U.S. Army's counterbattery systems, he adds. "There were 457 companies total with U.S. contracts in 2012 radar technology and/or services. Raytheon is by far the largest radar producer in the U.S., winning contracts totaling \$1.39 billion in 2012, while Lockheed Martin and Northrop Grumman were second and third respectively. Raytheon has been number one the last three years."

... U.S. radar contracts for 2012 totaled \$4.26 billion, an increase of almost a \$1 billion over 2011 and about \$1.5 billion over 2010 numbers.

The robust radar market and the focus military embedded system suppliers have on radar products led us to gear our content this issue toward radar technology. Our Special Report section's lead article covers general radar trends such as dismount detection, the Lockheed AN/TPQ-53 (Q-53) counterfire target acquisition radar (pictured on our cover this edition), and also looks at how Lockheed Martin engineers are mitigating the challenges wind farms create for long-range radar systems. Also included in the Special Report section is an article from Dan Kinney and Andy Johnston of Parker Aerospace on how two-phase cooling meets thermal management challenges in modern radar applications.

The lead article in our Mil Tech Trends section looks at how radar and electronic warfare designers are getting around poor-bandwidth technology by placing the processing power of a ground station next to the sensor on the platform. This paradigm enables data analysis and exploitation to be performed before data is sent to the ground on slow RF links, enabling real-time actionable intelligence to be sent to the warfighter. The article covers how FPGAs and commercial processors are driving radar and electronic warfare sensor processing designs.

Mil Tech Trends also includes two articles on Modular Open Systems Architecture, or MOSA. In the first article, Michael Stern of GE Intelligent Platforms talks about how to exploit MOSA software for high-performance ISR and signal applications. The second article, written by Chris Lewis and Alton Graves of Mercury Systems, covers how MOSA enables flexibility and cost savings for electronic warfare digital receivers. Also in this section, Jeff Malacarne of Barco contributed a piece on how "10 GbE enables real-time remote desktops for C4ISR." Meanwhile, in our Industry Spotlight section, Rodger Hosking of Pentek discusses how new Virtex-7 FPGA technology boosts radar performance.

In future radar designs, keep an eye out for InfiniBand. The switched fabric created a buzz at the Embedded Tech Trends (ETT) conference in Long Beach, CA, in January, where CSPI, GE Intelligent Platforms, Mercury Systems, and others in attendance launched new products based on the standard. InfiniBand along with 40 GbE will be implemented for radar and other intensive signal processing applications as both have longterm road maps, speed, and low latency, noted Marc Couture of Mercury Systems during ETT.

John McHale imchale@opensystemsmedia.com

# Radar's brave new world: OSA

By Charlotte Adams

A GE Intelligent Platforms perspective on embedded military electronics trends

But high performance has not always gone hand in hand with openness. Until recently, the best results in radar were achieved through proprietary software and hardware, which customers preferred even though it might lock them into particular vendors. Programming was difficult because the parallel execution so necessary for radar processing had to be built in at the application level. If six processors were required, six programs had to be written, each of which made calls to the math and communication libraries. These programs were difficult, time consuming, and expensive to write as well as challenging to upgrade. But these days OSA- and open standards-based software tools can change this paradigm.

### Radar: Shift to OSA

As technology evolved - spurred by the consumer market -Commercial Off-the-Shelf (COTS) and OSA hardware and middleware products (as well as the toolkits supporting them) reached the volume and acceptance level required to support shifts in the design of compute-intensive applications such as radar. Open architecture means that necessary programming interfaces are available and published, giving rise to a greater wealth of competing solutions, easier interoperability, and lower life-cycle costs as compared to proprietary solutions. High-performance middleware also means that some of the parallelization required by sensor applications – and previously done manually - can now be executed automatically through such aids such as signal processing and math libraries.

At the programming level, OSA approaches have caught up with proprietary systems through middleware such as VSIPL++, the latest version of the Vector Signal Image Processing Library. Application development toolkits have incorporated such middleware and other advances to make it easier for customers to use these OSA technologies.

### Pentagon buy-in

The Pentagon acknowledged these trends in 2010, when Under Secretary of Defense Ashton Carter called for the use of OSA as part of acquisition reform. This high-level support has flowed down to new procurements and upgrades. After all, since new hardware will make proprietary applications obsolete, customers might as well migrate to open systems middleware, too. Additionally, radar systems already had begun to reflect the technology shift before the Carter memorandum. MIT Lincoln Lab, for example, has employed the Radar

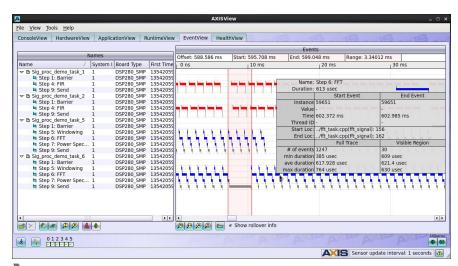

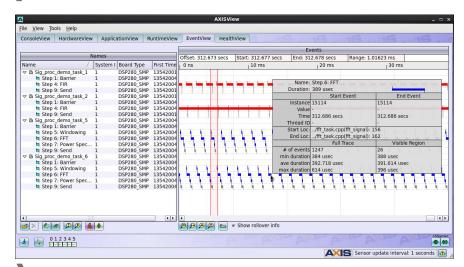

Figure 1 | GE's AXIS software development environment enables the rapid development of OSA radar applications on hardware platforms like the HPEC Starter System.

and the modernization of radars at the Kwajalein Missile Range.

The emphasis on OSAs in radar development continues. Requests For Information (RFIs) for new radar systems and upgrades are asking for open standards middleware technologies such as VSIPL++ and the open source Linux operating system.

One obvious way to lessen the difficulties of moving from a proprietary to an OSA-based radar system is to use software development suites with built-in OSA standards. These frameworks help developers meet deadlines by using math and signal processing functions such as the Fastest Fourier Transform in the West FFTW), VSIPL and VSIPL++, and data movement libraries such as Message Passing Interface (MPI) and Data Distribution Service (DDS).

Toolkits for radar system migration or design are available from multiple vendors. GE's Advanced Multiprocessor Integrated Software (AXIS) environment, for example, includes math libraries, visualization tools, and interprocessor communications optimizers that run on multiprocessor boards - even hybrids combining traditional and highly parallel chip architectures (Figure 1). The software suite also gives programmers access to standard middleware such as MPI, OpenFabrics Enterprise Distribution - or OFED, and VSIPL++. (MPI integration into the AXIS toolkit is expected in the near term.)

Toolkits also can accelerate radar application development by helping to partition code across potentially hundreds of processors. Then programmers can assess software performance visually, viewing a system as it is running to check the efficiency of the code and whether it's meeting its real-time constraints.

### Low pain, high gain

The transition from proprietary systems to open systems architectures, assisted by the latest standards-based software tools, should be relatively painless for radar systems engineers and should lead to greater system performance, programmer productivity, and cost-effectiveness.

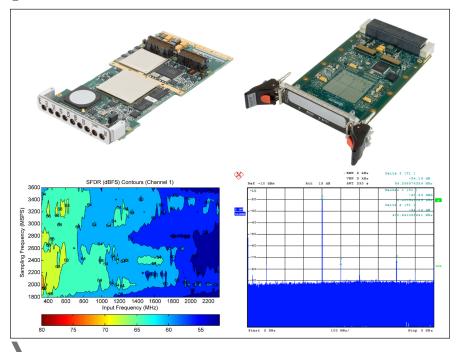

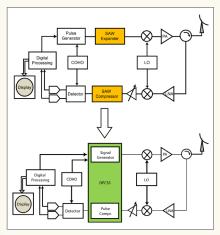

# SiGe-based ADCs/DACs double COTS **Electronic Warfare processing performance**

By David Jedynak An industry perspective from Curtiss-Wright Controls Defense Solutions

New ADC and DAC technology based on Silicon-Germanium (SiGe) promises unprecedented levels of functionality and capability for demanding signal processing applications. These new devices, which bring the advantages of SiGe to rugged deployed military systems for the first time, can deliver 2x the performance of currently available ADC/DAC devices, establishing a new class of processing performance for defense and aerospace applications. When deployed on open architecture platforms utilizing OpenVPX COTS boards with latestgeneration FPGAs, the new SiGe-based technology will provide an ideal platform for radar, SIGINT, and EW applications.

### New levels of performance

These types of EW applications require a balance between speed and resolution. Compared to earlier designs, these new SiGe-based ADCs/DACs, supplied by vendors such as Tektronix, feature higher sample rate performance. They leverage high-performance data conversion techniques to optimize device performance characteristics such as calibration, power, and signal/noise ratios. These ADCs, for example, deliver the best speed and Effective Number of Bits (ENOB) currently available from a commercial device. An additional advantage of SiGe-based devices is their low latency, an important feature for bandwidthsensitive EW applications.

Until recently, COTS ADC devices on the market have topped out at 3 GSps at 8 bits of resolution. In the past few years though, we've begun to see devices that can perform at up to 6 GSps at 8 bits. The new SiGe-based generation of ADCs is delivering the next big performance leap, doubling bandwidth speeds up to 12 GSps. For EW applications, the benefit is straightforward: The higher sample rates and associated bandwidth ensure better spectrum coverage and improved Probability Of Intercept (POI) for signals of interest. In addition, the performance

of these 8-bit parts surpasses off-the-shelf 10-bit ADCs in terms of Spurious Free Dynamic Range (SFDR). SFDR is a measure of the performance of the ADC, and higher SFDR ensures improved identification of signals of interest in a crowded spectral environment. Typically, a first pass of the spectrum segment is done at high bandwidth to pull in as much data as possible to obtain areas of interest to analyze, after which a higher-resolution, lower-bandwidth solution is leveraged to focus on specific targets. As warfighters see a far greater range of the spectrum, more lives are saved and mission success probability is increased because of faster, more accurate identification of threats and improved response options.

With this new generation of ADCs and DACs, EW system designers get increased bandwidth with sufficient resolution. It's a win-win with high-quality signal identification and improved immunity from noise that supports realtime analysis of larger amounts of data. While it's possible to obtain ADCs that operate at 14- to 16-bit resolution rates. these devices typically sample in the hundreds of Msample range, far below the 12 GSps rates at 8 bits now reachable.

SiGe-based ADCs/DACs also deliver lower power performance (as measured in Watt/GHz). In addition to their higher speed and lower power, these ADCs/ DACs also offer reduced leakage current and less sensitivity to temperature fluctuation, which becomes more critical in EW electronics as process architectures shrink.

### Faster I/O devices meld with OpenVPX and FPGAs

These faster ADCs and DACs can be readily built into rugged open architecture OpenVPX-based EW systems using FPGAs to perform high-speed algorithm processing in the digital domain; this paradigm minimizes the need for performing downconversions or other filtering stages that would typically be

Figure 1 | Tektronix Component Solutions' SiGe-based ADC provides 12.5 GSps digitization performance to the TADF-4300 module.

handled in an external analog tuner logic, slowing down performance and requiring additional on-board components that use valuable board real estate and add unwanted heat.

The new ADC/DAC components can be deployed on OpenVPX hosts so that the system designer has the flexibility to swap out different front-end configurations as required while maintaining a common back-end and software interface to the FPGA to address different types of applications. An example of an OpenVPX board that delivers the latest generation of devices is Curtiss-Wright's rugged CHAMP-WB-DRFM 6U card set, combining a Tektronix TADF-4300 module featuring a SiGe-based 12.5 GSps 8-bit ADC and a 12 GSps 10-bit DAC (Figure 1), on a Xilinx Virtex-7 FPGA-based 6U VPX card, the CHAMP-WB. This modular design approach actually provides designers with two levels of modularity or reconfigurability: The first level is the ability to swap out different mezzanines as needed. and the second level is the inherent reconfigurability of the FPGA itself. This serves to benefit today's cutting-edge EW applications.

> David Jednyak **CTO/COTS Technologies Curtiss-Wright Controls Defense Solutions** www.cwcdefense.com

# Static analysis exposes latent defects in legacy software

By Paul Anderson

When migrating from a legacy softwarebased system to new technology, it is important to be able to reuse as much code as possible. Even if such code has been tested thoroughly and has proved reliable in practice in the old system, it might still contain latent bugs. Those bugs might have never been triggered in the legacy system because of very specific properties of that system such as the toolchain used to compile the code, the processor architecture, or the host operating system. When ported to a new system where those properties are different, the latent defects might be manifest as harmful bugs. But the good news is that advanced static analysis tools can flush out these latent defects to help combat the challenge.

### Updating the system, revealing coding flaws

One of the most important motivations for migrating legacy systems is to take advantage of advances in hardware technology since the original system was first deployed. Probably the most common benefit is increased performance because of the adoption of a newer and faster processor. This is also the single most significant change from the perspective of the code. The new processor can have a different bit width, or endianness, and the number of available cores can be different. During code porting from the old platform to the next, much of the recoding effort will go into adapting the code to those differences.

### Compilers, toolchains, and latent bugs

There are many other less obvious differences than implementing a new processor, and these subtle nuances can be easy to overlook. Take, for example, the toolchain used to compile the code. On the face of it, this should not make much of a difference. After all, if the code was written to be ANSI C compliant, and if the compilers claim to

support ANSI C, then surely the code will have the same semantics when compiled by either compiler? Unfortunately not. The C and C++ standards are riddled with clauses that are "compiler dependent," meaning that the standard does not dictate exactly how to compile certain constructs, and the choice is up to the compiler writer. Many of these are obvious and well-known to programmers, such as the order in which operands are evaluated, but others are very subtle. A latent bug might be harmless on the legacy system because the compiler chooses to compile it a particular way, but hazardous on the new system because the new compiler makes a different choice.

"Compilers are programs too, of course, and are themselves not free of defects. A recent study of C compilers found code generation defects in every compiler they tested."

Compilers are programs too, of course, and are themselves not free of defects. A recent study of C compilers found code generation defects in every compiler they tested[1]. The treatment of the volatile keyword, which is of vital importance in embedded safety-critical software because it is frequently used to read sensor data, is especially prone to compiler errors that cause changes to sensor values to be silently ignored. A program's correct functioning might even come to rely on such flaws.

### Another danger zone: Standard libraries

Another subtle software migration difference that can cause latent defects to become hazardous involves the standard libraries that interface to the operating system. One might hope that such libraries would be consistent across

platforms, but this is rarely so. The most significant difference is with respect to error handling. A new platform can have completely different failure modes than the legacy platform, and the code might need to be changed to be able to handle those differences. Worse still, error cases appear to be very badly documented, according to a recent study[2].

### Static analysis wins out, complements traditional testing

Clearly, any legacy migration project must include a significant amount of time for testing the software in its new incarnation. However, test results are only as good as the test inputs. If a test case fails to exercise a path on which a bug occurs, that defect might go undetected. Generating new test cases is expensive too. Hence, a sensible tactic to flush out these latent defects is to use advanced static analysis tools as part of the legacy transformation effort. Such tools are capable of finding defects such as those described herein, including those that depend on platform subtleties. They are especially good at finding concurrency defects such as data races that are exceedingly difficult to find using traditional testing methodologies. They are also good at finding instances of code that, while not definitively wrong, is highly correlated with errors or is particularly risky when ported to a different environment.

### References

- [1] Finding and Understanding Bugs in C Compilers, Xuejun Yang, Yang Chen, Eric Eide, John Regehr, 2011. www.cs.utah. edu/~regehr/papers/pldi11-preprint.pdf

- [2] Expect the Unexpected: Error Code Mismatches Between Documentation and the Real World, Cindy Rubio-González, Ben Liblit, 2010. www.eecs.berkeley.edu/ ~rubio/includes/paste10.pdf

Paul Anderson is VP of Engineering at GrammaTech and can be contacted at paul@grammatech.com.

- Enginasion™ solves some of the most difficult technical problems involving process control, manufacturing automation, and product development, providing clients with electronic, mechanical and software engineering services from concept to production. For two decades, Enginasion (formerly Industrial Automation Systems) has been an invaluable partner to companies in the Industrial, Medical Technology, Military and Pharmaceutical sectors that need a sophisticated yet affordable engineering resource to help them overcome critical hurdles related to automation, control electronics, embedded software, and/or integrated product development. Since 1991, the Company has been providing key elements of successful R&D projects, manufacturing processes, and new high-tech products at innovative companies in the Northeast U.S. Enginasion provides the following resources:

- Test calibration and equipment designed with the operator in mind. Virtual instrument software using touch screens makes operator control fast and inexpensive. We integrate off-the-shelf and custom electronic and physical components with personal computers to create sophisticated test equipment at minimal cost.

- Product development, from tiny watch-sized electronics to highly specialized powder dispensing devices to large networked systems, Enginasion can handle the electronic design and PCB layout, real-time software, packaging, production prototypes, low-volume production test equipment and documentation for large-scale production.

- Process control systems for test or manufacture—measuring and controlling parameters such as machine movement, particle density, electrical charge, temperature, humidity, pressure, flow rate, Ph, viscosity, and droplet size, using embedded controllers and PLCs communicating via CAN, I2C Modbus, Bitbus, Ethernet, Firewire, Intellution or any other bus or network protocol.

- Quality control systems that turn quality measurements into real-time or manual process feedback, using custom data-gathering electronics, bar-coding, touch memories, RFID, statistics, reports and real-time process controls.

- Clients of Enginasion include "big" and "little" companies—some of whom have in-house engineering resources, and some of whom do not. Enginasion has helped clients in the Industrial, Medical Technology, Military and Pharmaceutical sectors to design and build hardware and software to monitor, measure and control mechanical and electrical systems. Enginasion specializes in solving the most difficult automation problems, applying ingenuity, in-depth understanding of physical phenomena and materials, and wide-ranging expertise in digital and analog electronics, software, user interfaces, networks, fluid controls, motion control systems and measurement techniques.

### **CONTACTS & KEY INFORMATION**

**Headquarters** 32 Almanac Way

West Boylston, MA 01583

+1 508 835 6353

Website www.enginasion.com

Sectors Industrial, Medical Technology, Served Military, Pharmaceutical

**Engineering** Controls...Sensors...Mechanics... Networks...Software...Patents... Resources **Electronics Engineering**

Some of the GE; The L.S. Starrett Company; **Select Clients** Subliminary Artworks; Renaissance Electronics; IMA-Served Nova® Packaging; MannKind

Sales David Bonneau, CEO Contact +1 508 835-6353 sales@enginasion.com

Media Ronald C. Trahan, APR Contact Ronald Trahan Associates Inc.

+1 508 359 4005, ext. 108

### **ENGINEERS WITH IMAGINATION**

### David Bonneau, BSEE

Chief Executive Officer

Skillsets: embedded development; metrology; sensors; process controls; systems arcitecture

### Roy Greenwood, BSEE

VP, Electronic Software & Hardware Design Skillsets: embedded systems, networking, electronics, systems software and architecture

### EXAMPLES OF CLIENT SOLUTIONS BY ENGINEERS WITH IMAGINATION

### **Test Calibration** and Equipment

Machine vision gauging . Multi-axis measuring machines • Spark gap analyzer, 32-channel, 1KV • Touch memory read/write probe • Watt-hour meter calibration/hi-pot/continuity test • Corrugation dimensional profiling • Alcohol sensor calibration • Digital caliper functional test, LCD, and calibration.

### **Product Development**

PC board text fixtures and software • Four-button mouse controller • Millimeter wave camera • Piezoelectric fluid nozzle control • Portable pepper spray delivery system • Wristwatch alcohol sensor/data logger • electronic nose • Multi-axis helmet shock data logger • Wireless hand tools • Portable, residential electrolyzer.

### **Process Control Systems**

Yarn tension velocity profiler • Fluid bed particle dispersion controls · Humidity chamber control · Low pressure fluid controls · Metering pump final test systems • High-power electrolyzer controls • PWM to Analog to PWM controller • Embedded software validator • Microgram powder dispenser array.

### **Quality Control Systems**

Electrolysis control systems • Hi-speed fiber analysis equipment • 0.001" grinding wheel gage • Sub-micron particle size analyzer • Vision-based LCD quality tester · Hi-capacity tablet imaging counter • Cosmetic tube label registration gauge • Military electrolyzer training simulator • Hi-pot test enclosures • Lab data-logging systems.

### **Special Report**

RADAR DESIGN TRENDS

# **Next-gen radars: Seeing through** the clutter

By John McHale, Editorial Director

Next-generation radar systems are improving accuracy in high-clutter environments such as littoral waters, wind farm locations, and slow-moving ground objects – and at faster than ever speeds, reducing the sensor to shooter cycle.

The TPS-77 portable long-range radar from Lockheed Martin Mission Systems & Training is mitigating, via sophisticated signal processing techniques, many of the false alarms caused by wind farms.

Military radar systems remain ever vigilant in their mission to detect superfast, incoming missiles and supersonic enemy fighter jets. High-speed threats are not going away, but military officials today also want radar systems to detect slower-moving objects on the ground or in shallow, littoral waters, requiring complex algorithms and signal processing techniques.

"Radar capability demands are trending toward dismount detection technology to detect people moving on the ground," says John Fanelle, Program Director, Radar Systems, Reconnaissance Systems Group at General Atomics Aeronautical Systems Inc. (GA-ASI) in San Diego. "We have incorporated this capability into our Lvnx Block 20A Multi-mode Radar and also added a maritime capability to crosscue the Electro-Optic/Infrared (EO/IR) ball on the Predator B/MQ-9 Reaper Remotely Piloted Aircraft (RPA) fleet to detect shorter-range maritime targets. A maritime mode for the radar is currently being developed to detect specific small items in the water. For the maritime mode we can leverage different algorithms that are available now. It's just a matter of getting them to work in real time."

Accurate, real-time information from radar and other sensors brought together in one picture helps save lives by reducing the sensor to shooter cycle - the time it takes for sensor data to reach a shooter, such as a UAS, fighter jet, tank, sniper, and so on, so it can eliminate a threat. "The trends are to more automation, smaller crews, radars that do multiple things, and radars that can talk to other sensors on the battlefield," says Lee Flake, Program Director for counterfire target acquisition radar programs at Lockheed Martin Mission Systems and Training. The AN/TPQ-53 (Q-53) counterfire target acquisition radar from Lockheed Martin is that type of radar. The system – which has 360- or 90-degree modes – reduces sensor to shooter time by acquiring the projectiles such as mortars, rockets,

and artillery while they are in the air, and sends information on their point of origin immediately, enabling it to destroy the object before it hits its intended target, Flake adds. "It all takes place in seconds."

The system, already operating in Iraq and Afghanistan, can be rapidly deployed, automatically leveled, and remotely operated as far as a kilometer away with a laptop computer or from a fully equipped climate-controlled command vehicle. "The radar uses a custom signal processing system designed by our partner, Syracuse Research Corp. (SRC) in Syracuse, NY," Flake says. "We designed the wireless component for the system. This approach is cutting edge and what the Army wants their sensors to do. When designing it, we started thinking 'What else can we add to this radar – what technology can we insert?' We are only beginning to attack the capability of this radar, which will be around for decades."

Adding capability without overhauling the system enables cost-effective and quick enhancements for meeting urgent requirements. "The beauty of our Lynx Block 20A is that it has enough capability to add these modes without redesigning the radar," Fanelle says (Figure 1). The multifunction radar functions in highresolution Synthetic Aperture Radar (SAR) and Ground Moving Target Indicator (GMTI) modes. Lynx provides photographic-quality images through rain, clouds, rain, smoke, dust, and fog, day or night. It flies on manned and remotely piloted platforms and has a range as long as 100 kilometers. In radar systems, situational awareness also is enhanced through 3D images. "Lynx has the ability to do 3-Dimensional (3D) targeting using radar imagery," Fanelle says. "With 3D targeting, you need longitude, latitude, and altitude. If you look at a target such as a ship at sea, longitude and latitude would suffice, but if the target is also high up in the mountains, on a plane, or a plateau, then you need to factor in altitude as well to properly fix the crosshairs on the target.

Very high precision is associated with 3D targeting, which enables the use of small weapons that minimalize collateral

Military radar users want quickly deployable systems that have more capability in smaller packages, that can run on less power, and that have more agility in how they are deployed - airborne, ground vehicle, man portable, and so on, says Pierre Poitevin, General Manager at FLIR Radars in Montreal. Time to market can be a challenge today because radar products are more complex and to deploy a system as quickly as possible requires a delicate balance between functionality in the product versus how soon a customer might want it. FLIR engineers developed a dual-mode ground surveillance radar - the Ranger R3D - that has a fast camera mode and a Doppler mode in a small form factor about 15 inches in height by 18 inches in diameter and less than 30 lbs. It consumes only 30 W and can be used in ground vehicles or man-portable applications for persistent surveillance.

Figure 1 | Photographic-quality imagery is generated by the multimode Lynx Block 20A radar system from General Atomics Aeronautical Systems. Inc. (GA-ASI).

### Open architectures

Quickly deployable systems with an architecture that can accommodate future capability upgrades need to leverage Commercial Off-the-Shelf (COTS) hardware and software as well as common standards. The use of common standards with products with high Technical Readiness Levels (TRLs) also reduces risk by encouraging interoperability.

"We leverage open architectures, and our radar compute engines use COTS components," Fanelle says. "Graphics Processing Units (GPUs) are creating a compute engine in the gaming industry that can do amazing stuff, and we are evaluating these devices to harness some of that power. The one thing the gaming industry doesn't have is environmental restrictions on its devices. We need to take a gaming GPU and make sure it can function within the environmental constraints in military applications."

"Implementing open architectures and common standards as part of our design process has allowed us to greatly reduce the number of parts for the same mission we were doing 30 years ago," says Rick Herodes, Business Manager for FPS-117/ TPS-77 Radar at Lockheed Martin Mission Systems & Training in Syracuse, NY. "All three of our surveillance radar products -TPS-77, the TPS-59 Marine Expeditionary Radar, and the FPS-117 long-range surveillance radar for the Air Force all use the same signal processing architecture. Treating all three as a product line enables us to leverage investment and support costs across multiple customers. For example, we use exactly the same parts in the TPS-77 as in the other radars such as the WILDFIRE FPGA boards from Annapolis Microsystems." (For more on COTS signal processing trends, see this edition's Mil Tech Trends coverage, beginning on page 20.)

### Mitigating wind farm challenges

High-clutter littoral waters are not the only tough environment vexing radar designers. The areas around wind farms, cause quite a few headaches for radar operators. Engineers at Lockheed Martin Mission Systems & Training say their TPS-77 portable long-range radar is mitigating many of the false alarms caused by wind farms through its architecture and signal processing techniques that leverage COTS computing systems.

"The basic problem with wind turbines is they are large and keep getting larger, are semi-metallic to protect the turbines from getting struck by lightning, and are high velocity. With the new generation of turbines, blade tip velocity can approach hundreds of miles an hour," says Chris Atherton, Technical Director for Long-Range Radar at Lockheed Martin Mission Systems & Training in Syracuse, NY. "These are all characteristics radar systems are designed to see, so they end up generating radar signatures that are orders of magnitude larger than a 747. Wind farms create complex clutter returns - zero Doppler (non-moving) from the tower and nacelle and non-zero Doppler (moving) from blade movement. The clutter returns

can increase false alarms and report aircraft where there are none. This clutter can also desensitize the radar such that it cannot detect aircraft in the vicinity of wind farms. The turbines also are typically located in the same areas as radars - high up and visible to get as much wind as possible. One mitigation technique used has been to prevent wind farms from being built in 'line of sight' with radars - causing conflict with wind farms development."

"To solve the wind farm challenges, we deploy a pencil beam radar system architecture in the TPS-77 transportable radar as opposed to a stack beam system," Herodes says. "The TPS-77 has the capability to produce a usable air picture within two hours of touching down at any given radar site to a range of 250 nautical miles. Many other longrange radars use multiple stacked beams to detect a target and estimate its height. Since stacked beam transmission is simultaneous, wind farms interfere with all the beams, confusing the radar's signal processing. Stack beam systems illuminate a much larger area as large as a horizon to 40,000 feet. Comparing that to a pencil beam illumination is like comparing a flood light to a laser beam."

"A pencil beam system like the TPS-77 focuses energy very narrowly while illuminating the targeted vicinity," Atherton says. "It localizes the wind farm and enables proper detection of an aircraft immediately around the wind farm. Because it is using focused energy, it is less likely to pick up the false alarms associated with the wind farm signatures. Transmission and processing are independent, preventing clutter in one beam from affecting another. An important result of the pencil beam architecture is the ability to detect uncooperative aircraft such as those that turn their transponders off so they cannot be seen. The fundamental architecture of pencil beam separates the returns and differentiates aircraft from the clutter returns.

"The TPS-77 3D Scanning Pencil Beam Phased Array system uses advanced clutter reduction techniques such as full monopulse processing, range adaptive MTI/Doppler processing, and advanced clutter mapping," Atherton continues. "Advanced signal processing techniques such as monopulse processing are necessary for detecting objects in littoral clutter and water/land transitions, which can change clutter characteristics fairly dramatically. Monopulse processing breaks a single beam into three beams and compares the results to determine target location. From the same transmission you can get many different looks, in many different pieces, and then integrate those pieces to get a better view of the returns. We only need a single return to get full stated accuracy of a radar system with monopulse processing. Other radars use multiple returns and employ averaging techniques, whereas monopulse is one hit, which is important for high-clutter environments around wind farms. Adaptive MTI and Doppler are excellent at suppressing targets of different speeds and velocities - like wind turbine blades." MES

### **Special Report**

RADAR DESIGN TRENDS

# Two-phase cooling meets the challenges of modern radar applications

By Dan Kinney and Andy Johnston

As radar systems' heat flux and thermal loads continue to increase alongside the pace of technology, two-phase liquid cooling is winning the race, beating more traditional methodologies (such as air-based and single-phase liquid cooling) to the finish line.

Customers today are seeking increased

capability and performance from advanced military systems such as radar and directed energy weapons. The ever increasing thermal load and heat flux (heat rate per unit area) of such systems are challenging the practical limits of conventional air-based and single-phase liquid cooling solutions. Thermal performance as well as Size, Weight, and Power (SWaP) constraints are also causing engineers to turn to more advanced cooling methods. Active Electronically Scanned Array (AESA) radar using high-density Transmit/Receive (T/R) modules require special attention. In fact, single-phase liquid cooling solutions are projected to be insufficient for future programs such as the Navy's Next Generation Jammer (NGJ) and Integrated Topside (InTop), both of which require AESA technology. For these reasons, two-phase liquid cooling technologies are gaining increased focus and attention, and will

allow engineers to overcome the design

challenges of advanced radar systems.

## Radar and its thermal management

In the '70s, radar systems had low heat flux and could generally be managed by blowing air over the heated surfaces. By the '90s, heat fluxes had increased enough to where air cooling was oftentimes no longer sufficient, prompting engineers to turn to closed-loop singlephase cooling systems using fluids such as Coolanol and mixtures of Ethylene Glycol and Water (EGW) or Propylene Glycol and Water (PGW). Although more complex and expensive from a system perspective, single-phase cooling systems have orders of magnitude greater capacity to remove waste heat as compared to air cooling. In aerospace applications, the advantage of liquid cooling over air cooling is amplified because of the decreasing density of air with altitude. For instance, a constant speed cooling fan at a 35,000 foot altitude delivers an air mass flow rate that is approximately 40 percent of the flow rate it can provide at sea level,

greatly limiting the cooling capacity of the system. Today, single-phase liquid cooling is well understood and is already in use on many military platforms including the F-22 and F-35. These cooling solutions have met the thermal demands of the presently fielded radar and tactical environment and have proven to be reliable and robust.

However, next-generation radar and jamming systems have thermal load and heat flux requirements that are starting to exceed the practical cooling capacity of single-phase liquid cooling solutions, necessitating the deployment of two-phase cooling systems. Two phase-cooling systems outperform single-phase cooling systems for two key reasons. First, two-phase cooling takes advantage of not only the higher heat absorption capacity of the liquid (that is, sensible heat), but also the heat absorbed when the liquid vaporizes (that is, the heat of vaporization). Second, two-phase flow in cooling

channels can support orders of magnitude higher heat flux than single-phase liquid flow at comparable coolant flow rates and thermal conditions.

### Two-phase cooling advantages, considerations

For some applications, a two-phase cooling system can operate with less than 50 percent of the flow rate required in single-phase systems. This directly translates into smaller pumps, fluid lines, and quick disconnects, and less pumping power, resulting in a much smaller thermal management system. The resulting higher energy dissipation capacity of a two-phase system is especially important for aircraft and pod applications where SWaP is critical.

Additional benefits of two-phase cooling for radar systems are performance characteristics such as improved range and target detection as well as reliability gains from surface temperature uniformity of cooled components. Surface temperature uniformity can be achieved by ensuring that the phase change from liquid to vapor takes place at near constant pressure (relative to system pressure), as the two-phase mixture flows over the heated surface or through cooling channels. As a result, the bulk temperature of the two-phase mixture stays nearly constant even as the mixture absorbs substantially more amounts of heat from adjacent electronic components. In contrast, in single-phase liquid cooling systems, the coolant temperature rises as it absorbs sensible heat, easily rising between 10 °C and 20 °C in practical applications, which can have significant impact on radar performance.

To understand better the advantages of two-phase cooling systems for radar applications, it is useful to consider Newton's law of cooling. Newton's law of cooling states that heat removed from a surface is proportional to the area of the surface and the temperature difference between the surface and the bulk fluid that cools the surface, or  $Q=h^*A^*(T_{wall}-T_{fluid})$ . The proportionality constant, h, is the well-known heat transfer coefficient, which has units of W/m<sup>2</sup>C. In radar cooling applications, an order of magnitude higher heat transfer coefficient can be achieved by employing two-phase flow than can be achieved with any practical singlephase cooling solution. For a desired heat removal rate through a fixed surface area, the higher heat transfer coefficient allows for a smaller temperature difference ( $\Delta T$ ) between the fluid and the surface being cooled. A smaller  $\Delta T$ ,

in turn, means that the coolant flowing through a cold plate can have a higher temperature while maintaining the same surface temperature. Radar system requirements have a worst case ambient temperature and maximum radar temperature (fixed system temperature difference); delivering hotter fluid to the cold plates allows thermal engineers significant system-level SWaP benefits such as designing smaller heat exchangers or eliminating vapor

# Small is the New BIG!

## We all know good things come in small packages.

Our Mini ATR design leverages Elma's proven COTS rugged construction techniques, yet delivers a smaller, lighter platform for space & weight constrained projects. It accommodates a wide range of embedded COTS architectures and payloads. It allows for DC and AC power variations, and custom 1/0 configurations.

One configuration combines a 3-slot OpenVPX<sup>TM</sup> backplane, and the option for a plug-in power supply and 2.5" storage tray. Elma will design the MIL-STD wiring and connectors specifically for your I/O needs. We can also help you with the payload — processors, audio/video, storage, you name it, we've got it. Elma is teamed with premier industry partners to provide the best solution for your application development needs.

Elma offers hundreds of system configurations using best in class products — from the backplane, to the SBC and storage, to high-end FPGA and GPGPU processors all integrated and tested from the one partner who pays attention to the smallest details.

Learn why the smallest details matter to Elma by visiting www.elma.com. Or by contacting us at **510.656.3400** or **sales@elma.com**.

compression cycles to condition the cold plate supply fluid. (For a detailed case study, see Sidebar 1.)

Ultimately, the decision on whether to adopt a two-phase system or stay with a single-phase solution will depend on a complete evaluation of system requirements along with its capabilities and operational limitations. On one hand, a well-designed and efficient two-phase

system will usually require more time to design and implement, and much of the design time comes from the increased complexity of thermal analyses required because of the nature of two-phase flow. In addition, two-phase systems, specifically systems using refrigerants, will have slightly different operating and servicing requirements compared to single-phase systems. These differences can, however, be managed and

are similar to servicing an air conditioner for a home or automobile.

On the other hand, the benefits of a smaller thermal management system have far reaching impact on the overall radar system. Consider, for example, the NGJ Broad Area Announcement (BAA), which states that 60 kW to 90 kW of power must be dissipated by the cooling system[1]. Allowing a

### Liquid cooling case study

The advantage of two-phase liquid cooling over single-phase cooling can be demonstrated in the following cold plate case study. Assume a 0.5 m x 0.5 m radar panel dissipates 30 kW of heat evenly distributed. This panel is to be cooled by a cold plate while maintaining the surface of the cold plate at 70 °C in a typical ground or shipboard 49 °C hot day environment. (Or this ambient temperature can be matched in stagnation temperature by flying around 30 kft at nearly mach 1.) The total system temperature difference ( $\Delta T$ ) is 70 °C - 49 °C = 21 °C. Let's also assume that half of the temperature difference is allotted to heat acquisition and half to the heat rejection. This sets the cold plate inlet temperature to 49 °C + 10.5 °C = 59.5 °C. Since much of the design challenge of liquid cooling is at the radar, the case study will focus on the cold plate only. Table 1 shows the results of a single-phase and two-phase cold plate design exercise.

Design cases 1-3 demonstrate the flow rates need to meet the surface temperature requirement in an easily machined cold plate with 150 channels of a 2.5 mm x 2.5 mm cross-section. Both the PAO and 60 percent Propylene Glycol and Water (PGW) cold plates require very high to unreasonable flow rates to achieve the necessary heat transfer coefficients to adequately cool the cold plate surface. Case 3 is the two-phase flow R134a cold plate, which requires only 7 Gallons Per Minute (GPM) at 1 psi pressure drop, an order of magnitude lower flow rate and pressure drop compared to Cases 1 and 2. Cases 1-3 help illustrate the system-level pumping improvement of two-phase liquid cooling that results from higher heat transfer coefficients at lower coolant flow rates and pressure drops.

To overcome the lower heat transfer coefficients, single-phase cold plates are typically designed to have the maximum heat transfer surface area with the penalty of higher pressure drop and a heavier cold plate. Cases 4 and 5 show the results of a more typical single-phase cold plate with folded straight fin with a 100-fold increase in number of fins and 3-fold increase in fin height over cases 1-3, constraining the design to a reasonable pressure drop and flow rate. Unfortunately, even at the highest fin density cases, neither of the single-phase cases is able to meet the surface temperature require-

ment and would require fluid conditioning through a vapor compression cycle, relief on the requirements, or dedicating more of the total system temperature drop to the cold plates at the cost of a larger heat rejection heat exchanger.

| Case   | Fluid                                               | H_fin | W_fin | Tin  | Tsurface | dP   | vdot | Convection coefficient | Fluid dT |  |

|--------|-----------------------------------------------------|-------|-------|------|----------|------|------|------------------------|----------|--|

| (-)    | (-)                                                 | in    | in    | С    | С        | PSID | GPM  | W/m <sup>2</sup> K     | С        |  |

| Machin | Machined: 2.5mm x 2.5mm (0.1in x 0.1in) channels    |       |       |      |          |      |      |                        |          |  |

| 1      | 60% PGW                                             | 0.1   | 0.1   | 59.5 | 70       | 11   | 66   | 7300                   | 2        |  |

| 2      | PAO                                                 | 0.1   | 0.1   | 59.5 | 69       | 49   | 179  | 7500                   | 1.5      |  |

| 3      | R134a                                               | 0.1   | 0.1   | 59.5 | 66       | 1    | 7    | 11300                  | 0.2      |  |

| Folded | Folded fin: 4331 Fins per meter (110 fins per inch) |       |       |      |          |      |      |                        |          |  |

| 4      | PAO                                                 | 0.3   | 0.005 | 59.5 | 77       | 43   | 22   | 2400                   | 12       |  |

| 5      | 60% PGW                                             | 0.3   | 0.005 | 59.5 | 75       | 20   | 11   | 5400                   | 12       |  |

Table 1 | Liquid-cooled radar case study results

Sidebar 1 | A cold plate case study illustrates the advantages two-phase liquid cooling offers versus single-phase cooling.

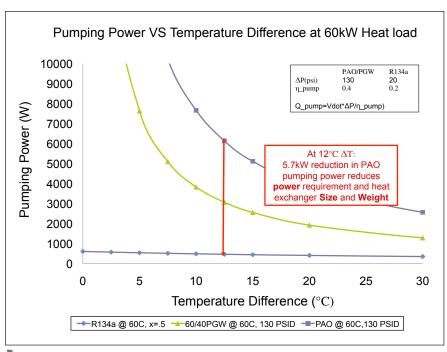

Figure 1 | System pumping power versus coolant temperature difference for single- and two-phase systems

single-phase system to operate with a (typical) 12 °C  $\Delta T$  at the cold plate, a Polyalphaolefin (PAO) system would require more than 3 kW of pumping power (Figure 1) compared to about 0.5 kW for an R134a two-phase system. Figure 1 also shows that a 60 percent EGW single-phase system requires more than 6 kW of pumping power under the same system requirements. The two-phase system, operating at a lower flow rate and pressure drop, can therefore use a smaller pump and heat rejection heat exchanger because less pump waste heat must be rejected.

# Matching the thermal management

As previously discussed, the demand for two-phase cooling systems, especially in advanced radar systems, continues to increase. Matching the right thermal management system to a particular application will yield the best solution for the warfighter. Understanding differences as well as advantages and disadvantages of the various types of thermal management solutions is essential. Fortunately, Parker Aerospace has been designing, building, and fielding robust single- and two-phase liquid-cooled systems for more than 20 years. Some of these systems have been developed

for fixed wing aircraft including manned and unmanned vehicles, rotorcraft, ground mobile vehicles, shipboard applications, and even missiles. Many of the next-generation systems, where heat loads and heat flux are increasing so dramatically, stand to benefit the most from efficiencies gained by twophase liquid cooling. MES

### Reference:

[1] Navy SBIR FY2008.1, Topic N08-035, Pod Mechanical Power Production, SBIR/STTR interactive topic information system, www.navysbir.com/08\_1/100.htm

Dan Kinney is the **Business Development** Manager for Parker Hannifin Corporation's Aerospace Group Thermal Management Systems (TMS) team.

Contact him at dan.kinney@parker.com.

**Andy Johnston** is an engineer for Parker Hannifin Corporation's Aerospace Group Advanced Development Team. Contact him at andrew.johnston@parker.com.

> Parker Hannifin Corp. www.parker.com

### Mil Tech Trends

SIGNAL PROCESSING TRENDS IN RADAR, SONAR, AND ELECTRONIC WARFARE

# **Fast processors**, **FPGAs fuel radar/EW** signal processing performance

By John McHale, Editorial Director

Radar and Electronic Warfare (EW) designers' thirst for more and more data is driving innovation at the signal processing level as embedded computing suppliers work magic with FPGAs and processors to create intelligent, fast sensor networks.

Radar onboard U.S. Navy Aegis-class ships uses PowerStream technology from Mercury Systems for radar signal processing.

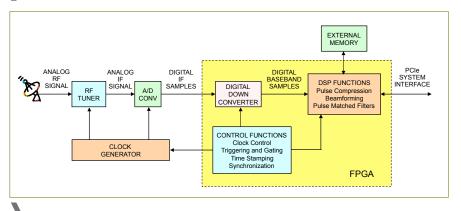

The need to know where and when the enemy will strike is no less important today than when the allies cracked the allegedly unbreakable German Enigma code during World War II. The only difference today is the sophistication of the technology on either side. Modern Electronic Warfare (EW) systems can detect, collect, and catalog just about every signal, while radar systems being developed today will be able to track dismounted personnel, small objects at sea, as well as enemy fighters. To make these capabilities possible, embedded computing wizards are packing as much processing power as possible at the payload level on the platform, right next to the sensor. They mix together components such as GPGPUs, multicore processors, FPGAs, and complex software algorithms in different configurations designed to meet the low Size, Weight, and Power (SWaP) requirements demanded by their military customers.

Sensor technology and the need for greater bandwidth are driving military electronics designs, especially in radar and electronic warfare applications, says Ray Alderman, Executive Director

of VITA. "What the processor and sensor technology enables us to do is absolutely incredible. Every aircraft has a signature. When we hit an enemy aircraft with radar we can figure out where it came from, destroy that location, then figure out where it is going and eliminate that destination as well. The only problem with increasing bandwidth on the sensors is the ability to stream data over the RF links is still poor. Therefore, the focus going forward is to move the processor next to the sensor."

"Department of Defense (DoD)-oriented customers want to be able to perform data exploitation onboard platforms to provide immediate actionable intelligence to the warfighter - avoiding delays and bottlenecks encountered when sending large amounts of data to a ground station," says Paul Monticciolo, Chief Technology Officer at Mercury Systems in Chelmsford, MA.

"In the past Intelligence, Surveillance, and Reconnaissance (ISR) systems were aimed at finding that particular truck or plane in an area of interest; now they are required to have the capability to pick individuals

out of a crowd," says Vincent Chuffart, Embedded Computing Specialist at Kontron in Poway, CA. "Today's sensor systems can detect everything, so integrators want to process that sensor data and extract all they can out of it at the sensor level before they transmit it to the warfighter." Kontron puts a lot into small form factor designs such as 3U VPX to handle the high-speed processing and meet SWaP requirements, he continues. There is a trend toward smaller and cooler systems, especially with the vast majority of upgrades in front of us being just a refresh of existing equipment, Chuffart adds.

"Users are trying to detect and decode complex radar or communication signals so they need more channels and these channels need to be accommodated simultaneously," says Rodger Hosking, Vice President at Pentek in Upper Saddle River, NJ. "An example would be a communication system that listens to multiple radios or communicates with multiple radios at the same time or a system that requires wider signal bandwidths for radar. Once these signals are digitized, higher data rates are required

to move the data, which puts a bigger load on the DSP engine to accommodate the data so it can keep up in real time." A higher level of system performance is required through more sophisticated signal processing techniques, higher-speed A/D converters to capture wideband signals, and faster FPGAs to do signal processing and process algorithms at higher rates, he adds.

### Harnessing commercial processor technology

Embedded computing companies are leveraging commercial processor technology - whether from Intel, NVIDIA, or other companies - to drive the performance of radar and electronic warfare systems. "FPGAs and GPGPUs are excellent for front-end sensor processing, but the SWaP characteristics of multicore processors are enabling us to provide the type of performance and analysis of data that is typically done in a ground station," Monticciolo says. "Some companies are working with mobile-class processors, but when you start doing massive correlations and graph-type processing, you need the performance of a multicore processor in a server-class

solution. This also guarantees code portability - being able to run the same code on a 1U server in the ground station and in a small embedded processing system up on the platform." Mercury has a high-performance embedded computing solution with their PowerStream technology performing radar processing onboard the Navy's Aegis-class ships.

"On Intel Architecture, the advent of AVX and the coming of AVX2 with a fused multiply-add pipeline are significantly improving the applicability of Intel devices to signal processing applications, as is the increasing performance of the integrated GPUs," says Peter Thompson, Senior Business Development Manager for high-performance embedded computing at GE Intelligent Platforms in Huntsville, AL. "Now that NVIDIA is shipping Kepler GPUs, we are seeing significantly better performance per watt than the previous generation Fermi offered. GPUDirect is helping us to reduce sensor-to-processor latency, and opening up some new applications such as EW that are time sensitive. The interconnects are keeping pace too - PCI Express Gen 3, 40 GbE, and 56 Gbps InfiniBand are starting to become available or are already out there, and are allowing us to keep the processing pipelines fed."

"For many EW and DSP applications, our customers have found that the Intel Core i7 processor provides them with the right balance of performance and SWaP," says Ben Klam, Vice President of Engineering at Extreme Engineering Solutions (X-ES) in Madison, WI. "The Intel Advanced Vector Extensions (AVX) supported by the Intel Core i7 processor provides excellent DSP performance with support for operations on 256-bit vectors."

### Managing power consumption and signal integrity

Processors do enable amazing applications, but also create serious headaches for embedded system designers with the heat they generate. Cooling the systems and keeping their power consumption low can be quite complex, especially as system designs trend toward smaller form factors.

"Two big challenges faced by embedded signal processing designers are power

consumption and signal integrity," says Denis Smetana, Product Marketing Manager for FPGA products at Curtiss-Wright Controls Defense Solutions in Ashburn, VA. "Devices continue to run faster, which requires more power. With so many high-speed signals, more exotic PWB material needs to be used along with special handling of high-speed traces and more detailed signal integrity and power integrity analysis. The super highspeed signaling is running the processors so fast that a lot of heat is being dissipated and as geometries keep getting smaller, leakage current gets bigger as a percentage of total power. And leakage current is very sensitive to temperature. This results in a significant power increase as temperature rises. Software/firmware also is needed to be able to utilize the larger processing performance."

"There are some applications with DSP performance requirements that exceed the capability of the Intel Core i7 processor where customers add GPGPUs or FPGAs into the mix, but the cost is high," Klam explains. "GPGPUs typically consume more power than embedded General Purpose Processors (GPPs), which in turn creates more heat that has to be dissipated. GPGPUs are driven by the consumer market, so product obsolescence can be a big problem for longlife embedded systems. And development is much more complex - software development in the case of GPGPUs and VHDL and software development in the case of FPGAs. We are also seeing a lot of demand for systems that require something smaller than 3U VPX can support," Klam says. "We have developed a small form factor system, the XPand6000 Series, that utilizes COTS components -COM Express, PMC/XMC, and SSDs - to enable customers to rapidly prototype and deploy small form factor solutions."

### FPGAs and the front end

For the front end of signal processing solutions - where the signals are received by the embedded computing system designers far and wide sing the praises of today's FPGAs, whether Xilinx or Altera, for enabling the capabilities of modern radar and electronic warfare platforms.

"We are seeing people wanting to put more components of their radar systems in an FPGA," says Jeff Milrod, CEO of

Bittware in Concord, NH. "Altera's Stratix technology is supporting this by placing a lot of floating-point capability in the front end. That way the system can aggressively integrate full imaging and even identify areas of interest before it sends data to the ground. FPGAs are needed because the rates are so high, now everybody seems to want direct RF conversion - so they get gigahertz sample rates flying and then handle them in the FPGAs."

Compared with a GPP, the FPGAs are much better suited for real-time embedded systems. The GPP, while very fast, is not well connected to I/O and does not do real-time data processing as well as an FPGA. Pentek's Onyx 71720 software radio module is used in radar, UAV, and communication signal processing applications and is based on the Xilinx Virtex-7 FPGA, used in radar and communication signal processing applications.

"FPGAs will continue to dominate digital signal processing for a myriad of reasons: mainly processor technology isolation and control of one's own IP the critical element in any real-time, signal processing platform," says Doug Patterson, Vice President of the Military & Aerospace Sector at Aitech in Chatsworth, CA. Aitech's military-grade 3U CompactPCI, 3U VPX, 6U VPX, and 6U VMEbus systems leverage FPGAs for radar and fire-control applications.

FPGAs process everything very fast and enable radar/EW integrators to have more control, to adapt and change their applications based on mission results, says Jane Donaldson, President of Annapolis Microsystems, in Annapolis, MD. "A major drawback with FPGAs for many is the expense of programming in VHDL, which adds labor costs and lengthens the design cycle," she continues. To reduce time to market and development costs on their WILDFIRE FPGA boards, Annapolis engineers use their CoreFire solution to program FPGAs. It enables software programmers working on GPPs to also program FPGAs, Donaldson adds.

"The combination of FPGAs with SBCs. GPGPUs, and multicore processors in one system is how requirements are trending," Smetana says. "For example, on the front end, FPGAs are well suited for parallel processing of sensor data, but then may feed the data to GPGPUs for additional parallel processing or multicore processors for sequential processing." Curtiss-Wright is working with Tektronix to improve performance for wideband, low-latency processing for Digital Radio Frequency Memory (DRFM),

electronic warfare, signal intelligence, and electronic countermeasure applications. Under the collaboration, Curtiss-Wright's CHAMP-WB ("Wideband") board will work with the Tektronix ADC/ DAC FMC module, the TADF-4300, to become the CHAMP-WB-DRFM utilizing a Xilinx Virtex-7 FPGA.

### FPGAs embracing ARM and OpenCL

"In the future we see embedded systems generally moving toward embracing ARM processor technology," Milrod says. "There is a huge user community and infrastructure, it is quite efficient, and the performance continues to improve dramatically with 64-bit now emerging. Although currently there is no ARM COTS community in the military, interest in these designs is exploding in the Linux world and could very well catch on in military designs. Both Altera and Xilinx are integrating ARM into all their FPGAs from now on. At BittWare, we've started to integrate them onto our high-end VPX boards. The ARM can handle housekeeping functions while the massive bulk processing onboard is handled by the FPGAs and/or floating point coprocessors such as our Anemone many-core processor that is based on Adapteva's Epiphany architecture.

"One standard that is getting interest in the defense community is the OpenCL

### Radar signal capture and collection speed enhanced by new software tool